热点资讯

91porn。com 2nm工艺大考倒计时

发布日期:2025-03-17 05:19 点击次数:141

2025年91porn。com,是先进制程代工场请托2nm及以下工艺的时刻点。2025年,2nm是人人半导体产业一大看点。跟着时刻的鼓励,2nm工艺“先驱们”的进展奈何?

台积电近期暗示,2nm工艺期间进展细致,将按期在本年下半年量产,产能在本年年底前有望达到5万片,以致有契机迈上8万片台阶。

三星暗示,其新一代自研移动处理器Exynos 2600将罗致自家的2nm工艺(SF2)代工,咫尺试产开始良率达到了瞻望的30%,正干涉大量资源,以确保其按时量产。

英特尔在官网上公开了其最顶端的Intel 18A制程工艺的先容,并称其还是“准备就绪”。

日本晶圆代工初创企业Rapidus暗示,其2nm晶圆厂建厂进程顺利,将在4月1日开始试产2nm,2027年开始量产。

台积电:进程超前,降本仍是首要难题

当作产业的领头羊,台积电在2nm芯片的研发和量产进程上一直处于行业开拔点地位,咫尺良率还是达到60%。

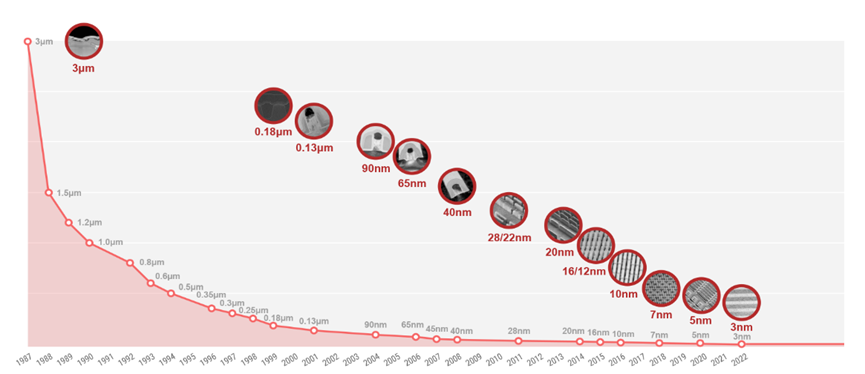

台积电的工艺演进图

早在2024年第一季度,台积电就在新竹宝山晶圆厂(Fab 20)顺利成就了2nm制程期间的试产线,这一举措记号着台积电在2nm期间领域还是取得了显耀进展。凭据台积电的蓄意,2025年下半年将是一个蹙迫的时刻节点,届时2nm芯片将施展进入批量分娩阶段。到2025年年底,若计入高雄晶圆厂(Fab 22)的产能,其2nm工艺的月产能瞻望将突破5万片。而在2026年年底,这一数字有望进一步攀升至每月12万至13万片。

同期,台积电为了称心2nm的量产需求,加大了对ASML的EUV光刻机的采购力度,在2024年就订购了30台,而况规划在2025年再订购35台,其中还包括ASML最新推出的High-NA EUV光刻机。如斯大界限的产能蓄意,为其在人人半导体市集的竞争中奠定了基础。

台积电的工场里面

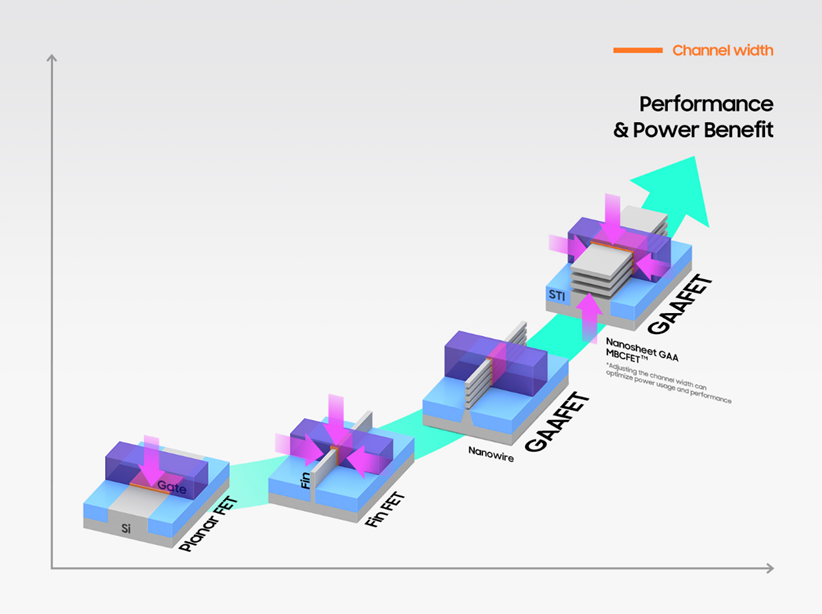

在期间方面,台积电在晶体管架构上,放弃了沿用已久的鳍式场效应晶体管(FinFET),转而罗致全环绕栅极场效应晶体管(GAAFET)期间。行家暗示,这种全新架构由一叠狭隘的硅带构成,每个硅带齐被一个栅极全场合包围。比拟FinFET,GAAFET对电流的适度更为详尽,极地面斥责了量子精真金不怕火效应,使得芯片在换取功耗下大要兑现更高的性能,或者在换取性能下大幅斥责功耗。例如来说,在移动开发中,罗致GAAFET架构的2nm芯片能让手机在万古刻运行高负载游戏时,发烧更少、电量破钞更慢,同期游戏画面的流通度和反应速率齐能得到显耀栽植。

台积电位于晶圆二十厂的2nm工艺主要分娩基地

此外,台积电还在2nm工艺中引入了多种新期间,例如NanoFlex DTCO(设想期间长入优化)期间的使用让路发者不错凭据不同的应用需求,生动聘用更高效的单位高度。若用于对能效条件极高的物联网开发芯片,可开发面积最小化、能效增强的更矮单位,让开发在极小的电量下也能万古刻安闲运行;罗致的第三代偶极子集成期间,赞助六个电压阈值档(6-Vt),范围达到200mV。这使得N型、P型纳米片晶体管的I/CV速率辩别栽植了70%、110%,优化了芯片的性能表现;愚弄全新的中间层(MoL)、后端层(BEOL)和远后端层(Far-BEOL)导线,让电阻斥责20%,能效更高。而况,第一层金属层(M1)当今只需一步蚀刻(1P1E)、一次EVU曝光即可完成,斥责了复杂度和光罩数目,不仅提高了分娩遵守,还斥责了分娩老本。此外,针对高性能蓄意应用,台积电还引入了超高性能的SHP-MiM电容,容量约莫每泛泛毫米200fF,不错获取更高的运行频率,称心了大数据处理、东谈主工智能磨砺等对蓄意速率条件极高的应用场景需求。

这些期间的空洞使用,让台积电的2nm工艺期间在性能栽植和功耗斥责方面展现出显耀的上风。台积电暗示,在性能栽植上,相较于现时粗俗应用的3nm制程,2nm制程在换取运行电压下,性能可提高15%,在同等性能下,功耗可斥责24%~35%。

尽管台积电的2nm芯片在期间上上风昭着,但在市集本质方面却濒临着老本不菲的难题。据了解,2nm芯片的制形老本极高,每片硅晶圆的报价高达3万好意思元,即使苹果这么的台积电的赤诚大客户,也会对2nm芯片的报价有所挂念。苹果原规划在iPhone 17系列中应用台积电的2nm芯片,但最终因老本原因,规划推迟至2026年的iPhone18系列上使用。

关于其他客户来说,这个影响只会被无穷放大,因此,如安在保证期间上风的同期,斥责老本,提高市集罗致度,是台积电过去需要惩办的重要问题。

三星:稳步鼓励,良率依旧濒临挑战

三星当作先进工艺的蹙迫推动者,一直在积极研发2nm工艺。在2024年三星晶圆代工论坛年度展览会上,三星公布了最新的半导体芯片工艺阶梯图91porn。com,晓喻将在2025年量产2nm芯片,并规划在2027年量产1.4nm芯片。

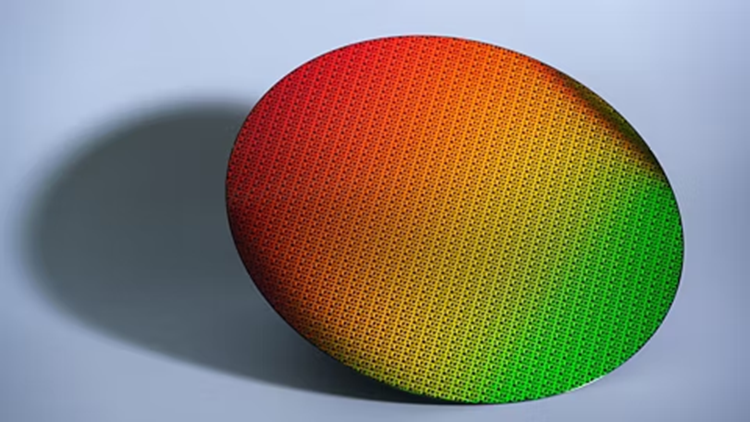

三星的职工展示晶圆

据了解,三星的2nm工艺布局了多个节点,其中第一代2nm工艺为SF2,后续又蓄意了SF2P、SF2X、SF2A和SF2Z等多个节点。咫尺,SF2的试产开始良率还是达到了瞻望的30%,三星正干涉大量资源,以确保其按时量产。

期间方面,三星的2nm工艺接续沿用了全环绕栅极(GAA)设想,三星暗示,传统的FinFET(鳍式场效应晶体管)期间慢慢暴表示局限性,如短沟谈效应加重,导致走电表象加多,进而影响芯片的性能和能效。而在GAA期间中,栅极大要从四个方针包围沟谈,相较于传统FinFET期间的三栅极结构,这种全环绕的设想极地面增强了对电流的适度才智。当晶体管尺寸收缩时,GAA期间不错有用减少走电表象,确保芯片在低功耗下安闲运行。

三星工艺封装期间演进图

除了GAA期间,三星在2nm芯片中还罗致了BSPDN(后面供电)期间,这一期间的应用相同为芯片性能的栽植带来了诸多公正。行家暗示,在传统的芯片设想中,供电收罗位于芯片正面,跟着晶体管数目的握住加多和尺寸的收缩,正面的布线空间变得愈发拥堵,布线堵塞问题日益严重,这不仅加多了电阻,导致功率损耗加多,还甘休了芯片性能的进一步栽植。

三星的BSPDN期间则将供电收罗转机到芯片后面,有用惩办了布线堵塞问题。该期间的旨趣是在芯片制造过程中,通过格外的工艺在芯片后面构建供电收罗,并愚弄硅通孔(TSV)期间兑现正面晶体管与后面供电收罗的通顺。这么一来,芯片正面就有了更多的空间用于信号布线,斥责了信号传输的侵犯,提高了信号传输的遵守,还能显耀栽植芯片的性能和能效。

三星合计,公司的2nm工艺与前代工艺比拟,其蓄意性能得到了显耀栽植。以三星自家的Exynos系列芯片为例,罗致2nm工艺的Exynos芯片在运行复杂的AI算法和大数据处理任务时,运算速率比拟上一代罗致3nm工艺的芯片提高了12%;在运行速率方面,在智高手机中,搭载2nm芯片的手机在掀开千般应用方法时,速率昭着加速,应用的启动时刻平均镌汰了30%傍边。

此外,三星官方数据自满,罗致2nm工艺后,晶圆的愚弄率提高了约20%,有用斥责了芯片的制形老本,使得三星在市集竞争中更具价钱上风。

尽管三星2nm芯片在期间层面取得了显耀突破,但三星永久濒临着良率不及50%的窘境,以致有报谈称,三星咫尺试产的2nm芯片良率仅在10%~20%之间。而且,良率问题不仅影响了三星2nm芯片的分娩遵守,还加多了分娩老本。由于大量芯片在分娩过程中出现劣势,无法达到及格程序,导致资源遽然和老本飞腾。

为了提高良率,三星遴选了一系列步伐。三星董事长李在镕亲身看望了ASML和蔡司等主要开发供应商,寻求工艺和良率改进的惩办有规划。然而,咫尺这些发愤尚未取得显耀效果,良率栽植仍濒临诸多羁系。

英特尔:性能担当,不顾处境宝石博弈

英特尔最近阅历了诸多难事,其代工业务的期间停滞更是被东谈主诟病已久,“牙膏厂”的名号在外甚是响亮。以致近期有音信称,台积电已向英伟达、AMD和博通建议,筹议入股一家结伴企业,来负责运营英特尔的代工场。

但英特尔这个宿将并莫得束手就擒,英特尔前任CEO基辛格曾十分硬气地暗示,英特尔的18A工艺期间是业界最开拔点的,优于台积电的N2工艺期间,而况最快于2025年上半年就能兑现量产。

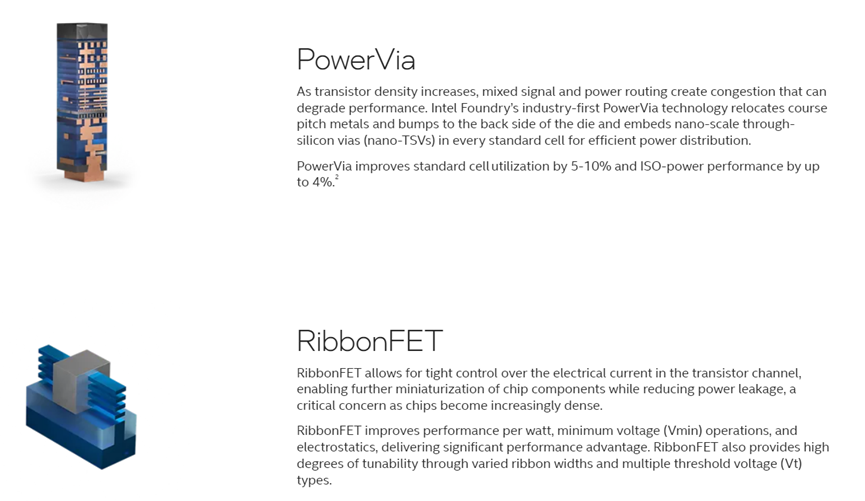

英特尔官网的贵府自满,与Intel 3工艺节点比拟,其18A工艺的每瓦性能提高15%,芯片密度提高30%。栽植的主要原因在于英特尔18A工艺期间领有两大中枢期间,辩别是RibbonFET晶体管期间和PowerVia电源传输期间。

RibbonFET晶体管期间是英特尔对Gate All Around(GAA)晶体管期间进行的一次创新,这亦然自2011年英特尔率先推出FinFET期间以来,在晶体管架构领域的又一次紧要变革。据了解,RibbonFET晶体管兑现了栅极对晶体管沟谈的全面环绕。这种全环绕栅极的结构带来了诸多上风。

从空间愚弄遵守来看,RibbonFET晶体管沟谈罗致垂直堆叠的表情,相较于传统FinFET晶体管的水平堆叠,减少了晶体管在芯片上所占据的空间。这使得在换取面积的芯片上,不错集成更多数目的晶体管,进一步提高了芯片的晶体管密度,为芯片性能的栽植提供了硬件基础。

在性能栽植方面,栅极对沟谈的全面环绕增强了对电流的适度才智。无论是在高电压照旧低电压环境下,RibbonFET晶体管齐大要提供更强的驱动电流,使得晶体管的开关速率得到栽植。这意味着芯片在处理多样数据和提醒时,大要愈加赶快地反应,从而提高了统共这个词芯片系统的运行速率和遵守。在运行复杂的东谈主工智能算法时,RibbonFET晶体管期间大要使芯片更快地完成矩阵运算等重要操作,镌汰了模子磨砺和推理的时刻。

而PowerVia电源传输期间是业界首个后面电能传输收罗,与三星的BSPDN(后面供电)期间一辞同轨,通过将电源传输收罗转机到芯片的后面,顺利地惩办了在传统的芯片制造工艺中,跟着芯片晶体管密度的握住加多,电源线和信号线在正面的布线变得越来越拥堵的难题。

据行家先容,在PowerVia期间的兑现过程中,开拔点按照传统工艺制造晶体管和互连层,然后将晶圆进行翻转并打磨,表示通顺电源线的底层。接着,在芯片的后面构建用于供电的金属层。这么一来,电源线和信号线被分离开来,芯片正面不错专注于信号传输,而后面则负责电源传输。这种全新的供电表情带来了多方面的上风。由于供电旅途愈加径直,减少了电源在传输过程中的电阻和电感,从而斥责了电压。

英特尔的测试收尾自满,PowerVia期间大要将平台电压下落优化30%以上,而使用PowerVia设想的英特尔能效核兑现了6%的频率增益和超越90%的程序单位愚弄率,不错让芯片在运行时获取愈加安闲和高效的电源供应,有助于提高芯片的性能和安闲性,减少了电源线和信号线之间的侵犯,提高了信号传输的质料。

商量机构TechInsights测算得出,英特尔18A工艺的性能值为2.53,台积电N2工艺的性能值为2.27,三星SF2工艺的性能值为2.19,这让业内对英特尔18A工艺期间的期待值拉满。英特尔如今还是在低谷中抗击,能弗成破釜千里舟拿下这一局,至关蹙迫。

Rapidus:后劲新东谈主,承载多方期待

日本很早就退出了提高半导体集成度的微型化竞争,咫尺日本工场最多只可分娩40nm的通用半导体居品。但近两年,跟着东谈主工智能等领域的爆火,日本政府也开始尝试进入先进工艺领域来分一杯羹。

2022年8月,日本政府结合了丰田、索尼、日本电气、铠侠、三菱日联银行等8家日本原土大企业,共同筹划了Rapidus公司,目的也十分宏伟,规划在2027年量产2nm芯片,兑现从40nm到2nm的飞跃。这关联词台积电、三星等行业巨头凭借多年的期间累积和无数的研发干涉,用了超越10年的时刻才兑现的期间突破。因此,这一目的也被日本视为过去从头成为“芯片强国”的重要。

妹妹自慰

关于Rapidus来说,日本政府还是予以了特等多的赞助,规划在2025年下半年,向Rapidus公司出资1000亿日元用作追加购买2027年开始量产所需的EUV光刻机等的资金。而况在2025年2月7日,日本政府通过内阁会议决定改进《信息处理促进法》和《特等管帐法》,以赞助Rapidus等半导体企业加速下一代半导体的量产。但要从建厂开始,想在短短几年内完成2nm的量产,难度显而易见。

期间开发方面,Rapidus聘用与早在2021年就顺利推出了人人首款罗致2nm工艺芯片的IBM联结,咫尺还是在GAA期间的应用上取得了突破。通过引入两种不同的聘用性减少层(SLR)工艺,保证了芯片在低电压环境下的高性能。这一工艺改进不仅简化了分娩经由,还栽植了良率,为大界限分娩打下了基础。

除了IBM,Rapidus还与比利时微电子商量中心(IMEC)达成了期间联结,进一步拓宽了期间研发的视线和资源渠谈。通过布置职工参与IMEC的商量格式,让Rapidus大要实时了解和掌持半导体领域的最新商量效果和期间趋势,为自己的2nm期间研发提供更多的想路和方法。

此外,在2024年12月,Rapidus从ASML获取第一台EUV机器。Rapidus社长小池淳义近日在演讲会上晓喻,公司首座晶圆厂IIM-1的开发进展顺利,还是装配了超越200台开发,Rapidus规划在2025年4月1日启动2nm GAA制程试产。有报谈称,Rapidus将与博通联结,规划在2025年6月向博通提供试产芯片。除了博通,Preferred Networks也奉求Rapidus代工2nm芯片,用于生成式AI处理。

不错看出,当下Rapidus的势头很猛,后劲很大,但IBM的2nm芯短暂间咫尺还仅仅实验室产物,转机为批量分娩的芯片工艺仍存在诸多期间难题,而且Rapidus当作“新东谈主”,底蕴不及,能否试分娩顺利,立时4月就能见分晓了。

· 产业不雅察:为何业界要拥抱2nm? ·

在半导体行业的发展历程中,工艺的高出永久是推动行业前进的中枢能源。比年来,东谈主工智能、物联网、大数据等领域的闹热发展,对芯片的条件愈发严苛,行业越来越期盼更高性能、更快运算速率、更粗劣耗的芯片,但芯片存在物理极限,只好握住精进工艺才智侵犯镣铐。

2nm工艺比拟现存的3nm工艺,在晶体管密度、性能和功耗方面齐有着显耀的上风,2nm工艺不错使芯片的晶体管密度提高约45%,性能栽植约15%,意味着芯片不错在更小的面积内兑现更多的功能,进而栽植芯片的运算才智。在智高手机中,更高的晶体管密度不错让芯片更快地处理多样数据,无论是运行多个应用方法,照旧进行复杂的图形处理,齐能愈加流通。在东谈主工智能领域,大量的晶体管不错赞助更复杂的神经收罗运算,加速模子的磨砺和推理过程,这关于推动东谈主工智能、高性能蓄意、物联网等领域的发展具有蹙迫意旨。

在功耗方面,2nm芯片相同表现杰出,比3nm工艺的功耗斥责约30%。高功耗不仅会导致开发的续航才智下落,还会产生大量的热量,影响开发的安闲性和使用寿命。2nm芯片的低功耗特质,不错延伸智高手机的电板续航时刻。关于数据中心这么的大界限蓄意场景,大量做事器产生的能耗是一个雄壮的老本,罗致2nm芯片的做事器,不错在降粗劣耗的同期,提高蓄意遵守,省俭能源老本。

更小的工艺使得芯片的体积不错进一步收缩,这关于那些对空间条件极高的开发,如可穿着开发、物联网传感器等来说至关蹙迫。更小的芯单方面积不仅不错让开发的设想愈加紧凑,兑现愈加微型化、轻量化的设想,还不错斥责分娩老本。在分娩过程中,相同大小的晶圆不错切割出更多的芯片,从而提高分娩遵守,斥责单个芯片的老本。

恰是由于2nm芯片具备如斯不凡的性能上风,人人各大芯片制造商齐纷繁投身于这场热烈的期间竞赛中。尽管各大企业2nm量产咫尺边临着诸多挑战,但例必齐会在本年交出答卷91porn。com,推动半导体行业进入一个新的发展阶段,也让统共这个词产业进入翻新期。